When it comes to the die bonding process for the assembly of RF power transistors, the most important metric is good thermal management. Ensuring high thermal conductivity of the bond between the chips and the transistor package is paramount to the longevity and performance of the device. Beyond that, the build requirements vary based on assembly approach and materials used.

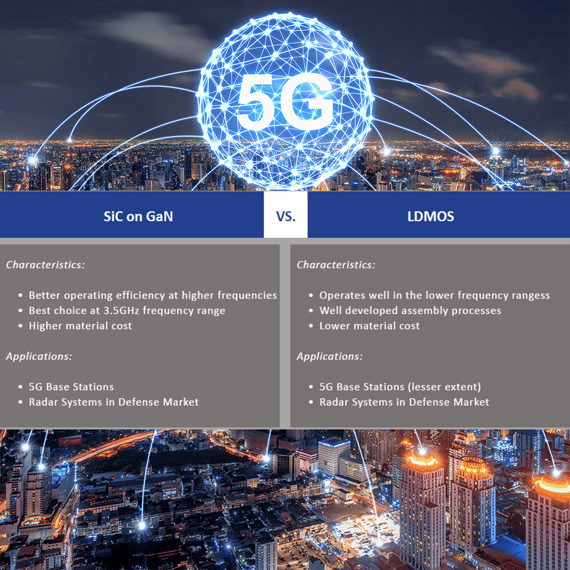

There are two major divisions in the RF power transistor designs as seen in Figure 1. The first separation is between transistors that use laterally diffused metal-oxide semiconductor (LDMOS ) die and those that use Gallium Nitride (GaN ) on Silicon Carbide (SiC ) die. GaN based transistors are able to operate much more efficiently at higher frequencies (3.5GHz level and above) but are generally more costly than their LDMOS based counterparts, which are a much more mature and therefor cheaper option. The 5G infrastructure does require these high frequency compatible transistors and will thus primarily necessitate GaN based solutions but LDMOS will certainly be implemented where able, due to its advantages of being a legacy product.

Figure 1: General overall differences between GaN and LDMOS transistors

The primary differences between GaN and LDMOS transistors are the thermal management requirements, die fragility, and die cost. As GaN technology is younger than LDMOS, the operating efficiencies are lower and thus require better dumping of heat to the package when in operation. This means that the thermal conductivity of the bond for GaN based transistors is extremely important and factors like voiding, solder quality, and bond line thickness play a large part in the overall performance of the device. The higher cost of GaN chips means that percent yield will likely take a higher precedence over sheer volume of production in comparison to LDMOS assemblies. Finally, the GaN die themselves are generally more fragile and susceptible to surface damage, which calls for greater care when handling and bonding.

The second most important division in transistor designs with respect to assembly of the devices is the die attach material used. Since high thermal conductivity is a strict requirement, eutectic bonding with alloys such as AuSn has been as staple for transistor builds. Pressure-less silver sintered paste is a strong alternative that boasts similar thermal conductivity of the bond with an offline “cure” cycle instead of the in situ reflow for eutectic bonding. The silver sintered solution generally leads to higher throughput but can introduce other potential issues.

In general, the eutectic bonding method for RF power transistors depends on several factors. Good solder quality is important as any oxides that are introduced into the bond or are present at bonding can inhibit the full thermal conductivity potential of the AuSn solder. Oxides form when either the solder – usually present as a preform or deposited on the back of the die – is exposed to oxygen in the air over a long period of time or when the solder is exposed to oxygen during the reflow step of bonding. These oxides not only limit thermal conductivity but can also lead to voiding, which is caused by gaps in the solder layer between the die and substrate. Voiding also greatly diminishes the thermal conductivity of the bond. Another important metric that comes into play with eutectic bonds is die surface quality after bonding. When using a die bonder to attach components with eutectic solders, it is preferable to “scrub” the component by commanding the bonder to move repeatedly in lateral directions while apply slight pressure in order to both break up oxides and spread the solder out in an effort to eliminate voids. However, due to the nature of eutectic alloys, there is a potential that the scrubbing can occur too early or too late in the reflow process thereby damaging the edges of the sensitive die. This is an even greater risk for GaN die where the surface is extremely fragile.

With pressure-less silver sintering, there is less concern with die damage but the emphasis on voiding remains paramount though the elements that result in voiding are instead centered on adhesive volume control, along with bonding force and bonding height repeatability. Adhesive volume control is necessary as inconsistent dispensing can lead to voids caused by an uneven bond line. Any gaps caused by poor dispensing control will also severely impact thermal conductivity. Bonding force control ensures consistent squeeze out as long as the adhesive volume is constant. Even more effective at producing quality silver sintered bonds is varying force, while ensuring bond height is repeatable. With the aid of extremely repeatable height measurement of the surface, the bond line can be set as the target instead of a force value, and the quality of the bond can be more tightly regulated

In order to ensure the aforementioned key metrics for RF Power transistors are properly maintained in an automated assembly environment, process control steps are required. To learn more, read our technical article: Balancing Throughput and Process Control for RF Power Amplifiers.

.png?width=480&name=Key%20Metrics%20of%20RF%20(2).png)

Figure 2: Wide array of RF Power Transistors on the market

For more information, download these resources:

Energy and Eco-Sustainability using Pressure-less Silver Sintering for RF Power Electronics: https://www.palomartechnologies.com/energy-and-eco-sustainability-using-pressure-less-silver-sintering-for-rf-power-electronics

Palomar 3880 Die Bonder: https://www.palomartechnologies.com/product/3880-die-bonder

----

Kyle Schaefer

Product Marketing Manager

Palomar Technologies, Inc.